범접할 수 없는 초격차…삼성전자, 12단 3D 패키징 최초 개발

뉴스1

입력 2019-10-07 10:52 수정 2019-10-07 10:52

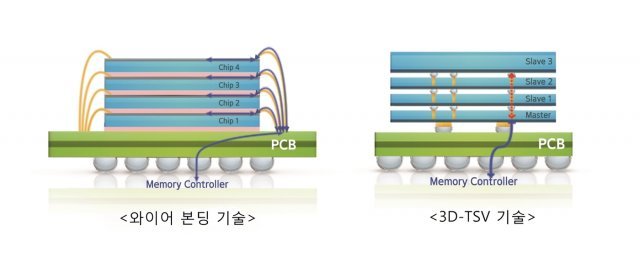

‘3D-TSV’와 ‘와이어 본딩’ 비교 이미지(삼성전자 제공)© 뉴스1

‘3D-TSV’와 ‘와이어 본딩’ 비교 이미지(삼성전자 제공)© 뉴스1삼성전자가 업계 최초로 D램 칩을 12단까지 쌓아 올리는 패키징 기술을 개발하면서 또 한번 경쟁업체가 따라올 수 없는 ‘초격차’ 벌렸다.

삼성전자는 ‘12단 3차원 실리콘 관통전극(3D-TSV) 기술’의 개발을 완료했다고 7일 밝혔다. 이 기술은 기존에 와이어를 이용해 칩을 연결하던 것과 달리 반도체 칩 상단과 하단에 마이크로미터(㎛, 머리카락 굵기의 20분의 1) 단위 직경의 전자 이동 통로(TSV) 6만개를 만들어 오차 없이 연결하는 첨단 패키징 기술이다.

‘3D-TSV’는 기존의 와이어 본딩 기술보다 칩들 사이에 신호를 주고받는 시간이 짧아져 속도를 높이고 소비전력도 획기적으로 줄일 수 있는 특징을 가졌다. 12단 3D-TSV는 종이의 절반 이하의 두께로 가공한 D램 칩 12개를 적층해 수직으로 연결하는 정밀성이 필요해 패키징 기술 중 가장 난이도가 높은 기술로 꼽힌다.

이번 기술 개발로 삼성전자는 기존 8단 적층 HBM2 제품과 동일한 두께(720㎛, 업계 표준)를 유지하면서도 12개의 D램 칩을 적층해 고객들은 별도의 시스템 디자인 변경 없이 더욱 높은 성능의 차세대 고용량 제품을 사용할 수 있게 됐다.

이 기술에 최신 16기가비트(Gb) D램 칩을 적용하면 업계 최대 용량인 24기가바이트(GB) 고대역폭 메모리(HBM) 제품도 구현할 수 있다. 이는 현재 주력으로 양산 중인 8단 8GB 제품보다 3배 늘어난 용량이다.

반도체 제조는 산화·노광·식각·증착 등의 ‘전공정’과 테스트와 패키징을 다루는 후공정으로 나뉜다. 어떻게 반도체를 패키징하느냐 따라 반도체의 속도와 전력 소모, 요령 등 성능과 생산 효율성을 높일 수 있어 삼성전자는 그동안 패키징 기술을 주요 미래 연구 과제로 꼽아 왔다.

백홍주 삼성전자 DS부문 TSP총괄 부사장은 “인공지능, 자율주행, HPC(High-Performance Computing) 등 다양한 응용처에서 고성능을 구현할 수 있는 최첨단 패키징 기술이 날로 중요해지고 있다”라며 “기술의 한계를 극복한 혁신적인 12단 3D-TSV 기술로 반도체 패키징 분야에서도 초격차 기술 리더십을 이어가겠다”고 밝혔다.

향후 상섬전자는 고객의 수요에 맞춰 12단 3D-TSV 기술을 적용한 고용량 HBM 제품을 공급해 프리미엄 반도체 시장을 선도해 나갈 계획이다.

(서울=뉴스1)

비즈N 탑기사

백일 아기 비행기 좌석 테이블에 재워…“꿀팁” vs “위험”

백일 아기 비행기 좌석 테이블에 재워…“꿀팁” vs “위험” 최저임금 2만원 넘자 나타난 현상…‘원격 알바’ 등장

최저임금 2만원 넘자 나타난 현상…‘원격 알바’ 등장 “배우자에게 돈 보냈어요” 중고거래로 명품백 먹튀한 40대 벌금형

“배우자에게 돈 보냈어요” 중고거래로 명품백 먹튀한 40대 벌금형 이렇게 63억 건물주 됐나…김지원, 명품 아닌 ‘꾀죄죄한’ 에코백 들어

이렇게 63억 건물주 됐나…김지원, 명품 아닌 ‘꾀죄죄한’ 에코백 들어 상하이 100년간 3m 침식, 中도시 절반이 가라앉고 있다

상하이 100년간 3m 침식, 中도시 절반이 가라앉고 있다- 김지훈, 할리우드 진출한다…아마존 ‘버터플라이’ 주연 합류

- “도박자금 마련하려고”…시험장 화장실서 답안 건넨 전직 토익 강사

- 몸 속에 거즈 5개월 방치…괄약근 수술 의사 입건

- 일본 여행시 섭취 주의…이 제품 먹고 26명 입원

- “1인 안 받는 이유 있었네”…식탁 위 2만원 놓고 간 손님 ‘훈훈’

1인 가구 공공임대 ‘면적 축소’ 논란…국토부 “면적 기준 폐지 등 전면 재검토”

1인 가구 공공임대 ‘면적 축소’ 논란…국토부 “면적 기준 폐지 등 전면 재검토” 삼성, 세계 첫 ‘올인원 AI PC’ 공개

삼성, 세계 첫 ‘올인원 AI PC’ 공개 “인구감소로 집값 떨어져 노후 대비에 악영향 줄수도”

“인구감소로 집값 떨어져 노후 대비에 악영향 줄수도” [머니 컨설팅]사적연금 받을 때 세금 유불리 따져봐야

[머니 컨설팅]사적연금 받을 때 세금 유불리 따져봐야 “만원으로 밥 먹기 어렵다”…평균 점심값 1만원 첫 돌파

“만원으로 밥 먹기 어렵다”…평균 점심값 1만원 첫 돌파- 고금리-경기침체에… 개인회생 두달새 2만2167건 역대 최다

- “한국판 마리나베이샌즈 막는 킬러규제 없애달라”

- 직장인 1000만명 이달 월급 확 준다…건보료 ‘20만원 폭탄’

- 엘리베이터 호출서 수령자 인식까지… ‘배송 로봇’ 경쟁 본격화

- 연체 채권 쌓인 저축銀, 영업 축소… 수신잔액 26개월만에 최저

![美-중동 석유공룡도 뛰어든 플라스틱… 역대급 공급과잉 우려[딥다이브] 美-중동 석유공룡도 뛰어든 플라스틱… 역대급 공급과잉 우려[딥다이브]](https://dimg.donga.com/a/102/54/90/1/wps/ECONOMY/FEED/BIZN/124642003.3.thumb.jpg)

![우리 집앞에도 ‘연트럴파크’ 생길까?…철도 지하화 사업의 모든 것[부동산 빨간펜] 우리 집앞에도 ‘연트럴파크’ 생길까?…철도 지하화 사업의 모든 것[부동산 빨간펜]](https://dimg.donga.com/a/102/54/90/1/wps/ECONOMY/FEED/BIZN_REALESTATE/124653245.2.thumb.png)